实验二 译码器和编码器

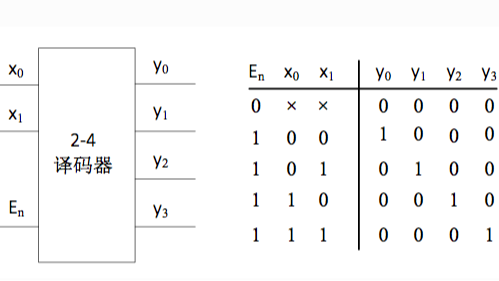

2-4译码器

.

├── constr

│ └── top.nxdc

├── csrc

│ └── test_our.cpp

├── Makefile

├── vsrc

│ └── top.v

├── top.v

├── vlt_dump.vcd

├── test_our.cpp

├── obj_dir

└── dump.vcd

├── constr

└── top.nxdc

top=topy (LD3, LD2, LD1, LD0)

x (SW1, SW0)en (SW2)

├── csrc

└── test_our.cpp

#include<nvboard.h>

#include<Vtop.h>static TOP_NAME dut;void nvboard_bind_all_pins(TOP_NAME* top);static void single_cycle(){dut.eval();

}int main(){nvboard_bind_all_pins(&dut);nvboard_init();while(1){nvboard_update();single_cycle();}}

├── test_our.cpp

#include "verilated.h"

#include "verilated_vcd_c.h"

#include "obj_dir/Vtop.h"VerilatedContext* contextp = NULL;

VerilatedVcdC* tfp = NULL;static Vtop* top;void step_and_dump_wave(){top->eval();contextp->timeInc(1);tfp->dump(contextp->time());

}

void sim_init(){contextp = new VerilatedContext;tfp = new VerilatedVcdC;top = new Vtop;contextp->traceEverOn(true);top->trace(tfp, 0);tfp->open("dump.vcd");

}void sim_exit(){step_and_dump_wave();tfp->close();

}int main() {sim_init();top->en = 0b0; top->x = 0b00; step_and_dump_wave();top->x = 0b01; step_and_dump_wave();top->x = 0b10; step_and_dump_wave();top->x = 0b11; step_and_dump_wave();top->en = 0b1; top->x = 0b00; step_and_dump_wave();top->x = 0b01; step_and_dump_wave();top->x = 0b10; step_and_dump_wave();top->x = 0b11; step_and_dump_wave();sim_exit();

}

├── vsrc

└── top.v

module top(x,en,y);input [1:0] x;input en;output reg [3:0]y;always @(x or en)if (en)begincase (x)2'd0 : y = 4'b0001;2'd1 : y = 4'b0010;2'd2 : y = 4'b0100;2'd3 : y = 4'b1000;endcaseendelse y = 4'b0000;endmodule

├── top.v

module top(x,en,y);input [1:0] x;input en;output reg [3:0]y;always @(x or en)if (en)begincase (x)2'd0 : y = 4'b0001;2'd1 : y = 4'b0010;2'd2 : y = 4'b0100;2'd3 : y = 4'b1000;endcaseendelse y = 4'b0000;endmodule

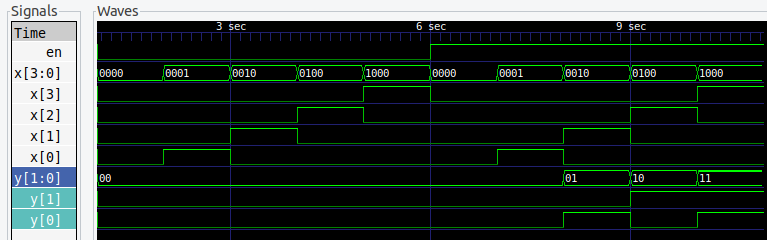

波形仿真

(1)编译

verilator -Wall --trace -cc top.v --exe main.cpp

(2)生成可执行文件make -C obj_dir -f Vtop.mk Vtop

(3)生成波形

./obj_dir/Vtop

(4)查看波形

gtkwave dump.vcd

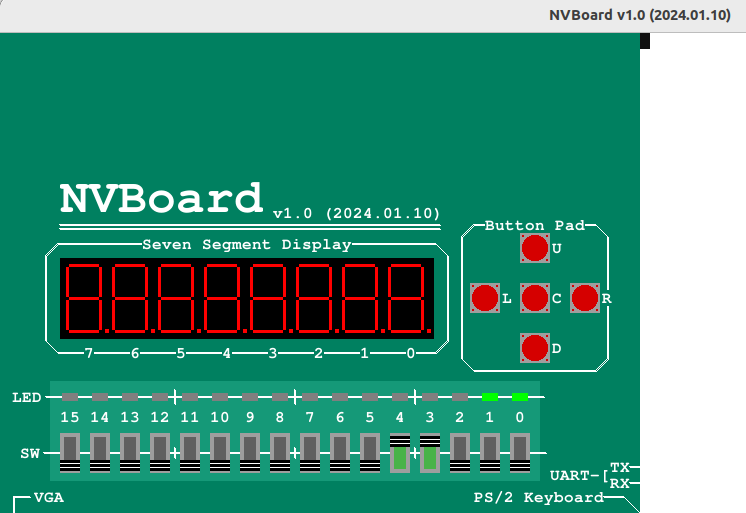

接入NVBoard

make

cd build

./top

4-2编码器

.

├── constr

│ └── top.nxdc

├── csrc

│ └── test_our.cpp

├── Makefile

├── vsrc

│ └── top.v

├── top.v

├── vlt_dump.vcd

├── test_our.cpp

├── obj_dir

└── dump.vcd

├── constr

└── top.nxdc

top=topy (LD1, LD0)

x (SW3, SW2, SW1, SW0)en (SW4)

├── csrc

└── test_our.cpp

#include<nvboard.h>

#include<Vtop.h>static TOP_NAME dut;void nvboard_bind_all_pins(TOP_NAME* top);static void single_cycle(){dut.eval();

}int main(){nvboard_bind_all_pins(&dut);nvboard_init();while(1){nvboard_update();single_cycle();}}

├── test_our.cpp

#include "verilated.h"

#include "verilated_vcd_c.h"

#include "obj_dir/Vtop.h"VerilatedContext* contextp = NULL;

VerilatedVcdC* tfp = NULL;static Vtop* top;void step_and_dump_wave(){top->eval();contextp->timeInc(1);tfp->dump(contextp->time());

}

void sim_init(){contextp = new VerilatedContext;tfp = new VerilatedVcdC;top = new Vtop;contextp->traceEverOn(true);top->trace(tfp, 0);tfp->open("dump.vcd");

}void sim_exit(){step_and_dump_wave();tfp->close();

}int main() {sim_init();top->en=0b0; top->x =0b0000; step_and_dump_wave();top->x =0b0001; step_and_dump_wave();top->x =0b0010; step_and_dump_wave();top->x =0b0100; step_and_dump_wave();top->x =0b1000; step_and_dump_wave();top->en=0b1; top->x =0b0000; step_and_dump_wave();top->x =0b0001; step_and_dump_wave();top->x =0b0010; step_and_dump_wave();top->x =0b0100; step_and_dump_wave();top->x =0b1000; step_and_dump_wave();sim_exit();

}

├── vsrc

└── top.v

module top(x,en,y);input [3:0] x;input en;output reg [1:0]y;always @(x or en)if (en)begincase (x)4'b0001 : y = 2'd0;4'b0010 : y = 2'd1;4'b0100 : y = 2'd2;4'b1000 : y = 2'd3;default : y = 2'd0;endcaseendelse y = 2'd0;endmodule

├── top.v

module top(x,en,y);input [3:0] x;input en;output reg [1:0]y;always @(x or en)if (en)begincase (x)4'b0001 : y = 2'd0;4'b0010 : y = 2'd1;4'b0100 : y = 2'd2;4'b1000 : y = 2'd3;default : y = 2'd0;endcaseendelse y = 2'd0;endmodule

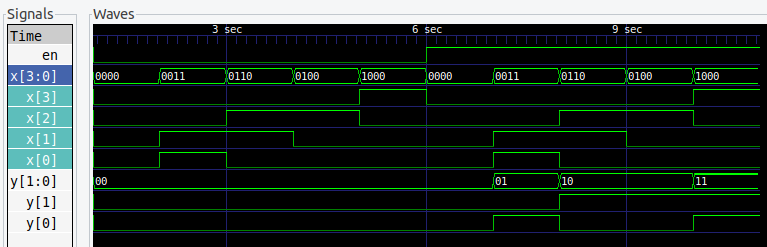

波形仿真

(1)编译

verilator -Wall --trace -cc top.v --exe main.cpp

(2)生成可执行文件make -C obj_dir -f Vtop.mk Vtop

(3)生成波形

./obj_dir/Vtop

(4)查看波形

gtkwave dump.vcd

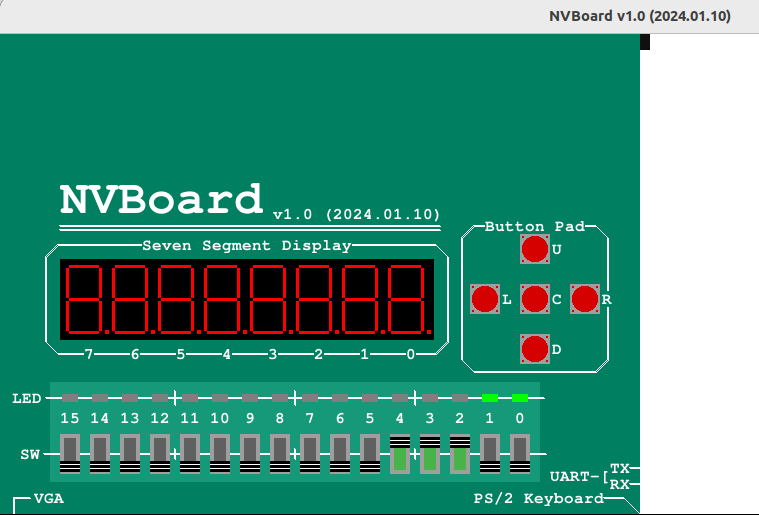

接入NVBoard

make

cd build

./top

4-2优先编码器

.

├── constr

│ └── top.nxdc

├── csrc

│ └── test_our.cpp

├── Makefile

├── vsrc

│ └── top.v

├── top.v

├── vlt_dump.vcd

├── test_our.cpp

├── obj_dir

└── dump.vcd

├── constr

└── top.nxdc

top=topy (LD1, LD0)

x (SW3, SW2, SW1, SW0)en (SW4)

├── csrc

└── test_our.cpp

#include<nvboard.h>

#include<Vtop.h>static TOP_NAME dut;void nvboard_bind_all_pins(TOP_NAME* top);static void single_cycle(){dut.eval();

}int main(){nvboard_bind_all_pins(&dut);nvboard_init();while(1){nvboard_update();single_cycle();}}

├── test_our.cpp

#include "verilated.h"

#include "verilated_vcd_c.h"

#include "obj_dir/Vtop.h"VerilatedContext* contextp = NULL;

VerilatedVcdC* tfp = NULL;static Vtop* top;void step_and_dump_wave(){top->eval();contextp->timeInc(1);tfp->dump(contextp->time());

}

void sim_init(){contextp = new VerilatedContext;tfp = new VerilatedVcdC;top = new Vtop;contextp->traceEverOn(true);top->trace(tfp, 0);tfp->open("dump.vcd");

}void sim_exit(){step_and_dump_wave();tfp->close();

}int main() {sim_init();top->en=0b0; top->x =0b0000; step_and_dump_wave();top->x =0b0011; step_and_dump_wave();top->x =0b0110; step_and_dump_wave();top->x =0b0100; step_and_dump_wave();top->x =0b1000; step_and_dump_wave();top->en=0b1; top->x =0b0000; step_and_dump_wave();top->x =0b0011; step_and_dump_wave();top->x =0b0110; step_and_dump_wave();top->x =0b0100; step_and_dump_wave();top->x =0b1000; step_and_dump_wave();sim_exit();

}

├── vsrc

└── top.v

module top(x,en,y);input [3:0] x;input en;output reg [1:0]y;integer i;always @(x or en) beginif (en)beginy = 0;for( i = 0; i <= 3; i = i+1)if(x[i] == 1) y = i[1:0];endelse y = 0;end

endmodule

├── top.v

module top(x,en,y);input [3:0] x;input en;output reg [1:0]y;integer i;always @(x or en) beginif (en)beginy = 0;for( i = 0; i <= 3; i = i+1)if(x[i] == 1) y = i[1:0];endelse y = 0;end

endmodule

波形仿真

(1)编译

verilator -Wall --trace -cc top.v --exe main.cpp

(2)生成可执行文件make -C obj_dir -f Vtop.mk Vtop

(3)生成波形

./obj_dir/Vtop

(4)查看波形

gtkwave dump.vcd

接入NVBoard

make

cd build

./top

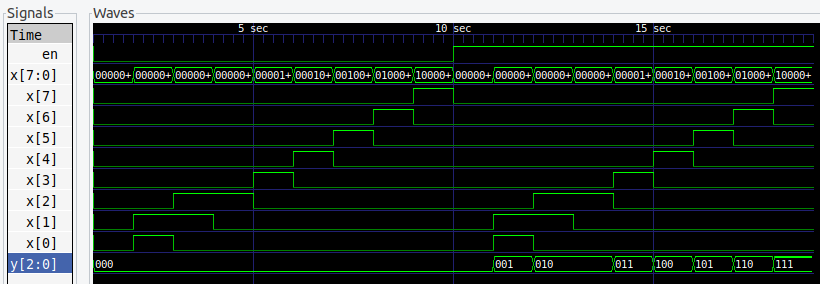

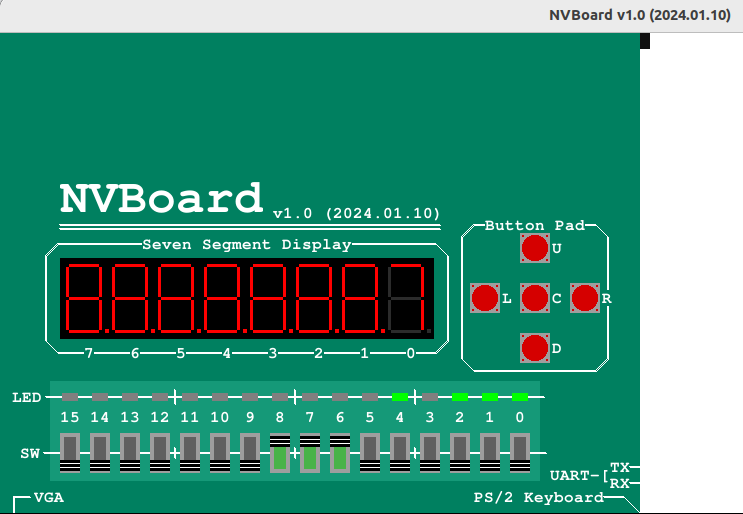

8-3优先编码器

.

├── constr

│ └── top.nxdc

├── csrc

│ └── test_our.cpp

├── Makefile

├── vsrc

│ └── top.v

├── top.v

├── vlt_dump.vcd

├── test_our.cpp

├── obj_dir

└── dump.vcd

├── constr

└── top.nxdc

top=topy (LD2, LD1, LD0)

valid (LD4)

x (SW7, SW6, SW5, SW4, SW3, SW2, SW1, SW0)

seg0 (SEG0A, SEG0B, SEG0C, SEG0D, SEG0E, SEG0F, SEG0G, DEC0P)

en (SW8)

├── csrc

└── test_our.cpp

#include<nvboard.h>

#include<Vtop.h>static TOP_NAME dut;void nvboard_bind_all_pins(TOP_NAME* top);static void single_cycle(){dut.eval();

}int main(){nvboard_bind_all_pins(&dut);nvboard_init();while(1){nvboard_update();single_cycle();}}

├── test_our.cpp

#include "verilated.h"

#include "verilated_vcd_c.h"

#include "obj_dir/Vtop.h"VerilatedContext* contextp = NULL;

VerilatedVcdC* tfp = NULL;static Vtop* top;void step_and_dump_wave(){top->eval();contextp->timeInc(1);tfp->dump(contextp->time());

}

void sim_init(){contextp = new VerilatedContext;tfp = new VerilatedVcdC;top = new Vtop;contextp->traceEverOn(true);top->trace(tfp, 0);tfp->open("dump.vcd");

}void sim_exit(){step_and_dump_wave();tfp->close();

}int main() {sim_init();top->en=0b0; top->x =0b00000000; step_and_dump_wave();top->x =0b00000011; step_and_dump_wave();top->x =0b00000110; step_and_dump_wave();top->x =0b00000100; step_and_dump_wave();top->x =0b00001000; step_and_dump_wave();top->x =0b00010000; step_and_dump_wave();top->x =0b00100000; step_and_dump_wave();top->x =0b01000000; step_and_dump_wave();top->x =0b10000000; step_and_dump_wave();top->en=0b1; top->x =0b00000000; step_and_dump_wave();top->x =0b00000011; step_and_dump_wave();top->x =0b00000110; step_and_dump_wave();top->x =0b00000100; step_and_dump_wave();top->x =0b00001000; step_and_dump_wave();top->x =0b00010000; step_and_dump_wave();top->x =0b00100000; step_and_dump_wave();top->x =0b01000000; step_and_dump_wave();top->x =0b10000000; step_and_dump_wave();sim_exit();

}

├── vsrc

└── top.v

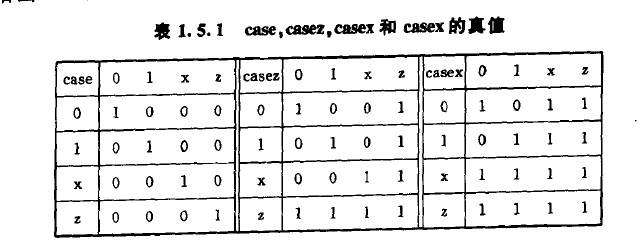

module top (input [7:0] x, // 8位输入input en, // 使能端output [2:0] y, // 3位编码输出output valid, // 有效指示位output [7:0] seg0 // 七段数码管输出

);// 实例化优先编码器priority_encoder_8to3 encoder (.x(x),.en(en),.y(y),.valid(valid));// 实例化七段译码器seg7_decoder decoder (.bin_in(y),.seg0(seg0));

endmodulemodule priority_encoder_8to3 (input [7:0] x, // 8位输入input en, // 使能端output reg [2:0] y, // 3位编码输出output valid // 有效指示位(至少有一个输入为1)

);always @(x or en) beginif (en) begincasez (x)8'b1???????: y = 3'b111; // 最高位优先8'b01??????: y = 3'b110;8'b001?????: y = 3'b101;8'b0001????: y = 3'b100;8'b00001???: y = 3'b011;8'b000001??: y = 3'b010;8'b0000001?: y = 3'b001;8'b00000001: y = 3'b000;default: y = 3'b000; // 全0情况endcaseendelse beginy = 3'b000; // 使能无效时输出0endendassign valid = en && (|x); // 使能且至少有一个1时有效

endmodule

└── seg.v

module seg7_decoder (input [2:0] bin_in, // 3位二进制输入output [7:0] seg0 // 七段数码管输出(共阳)

);reg [7:0] seg;always @(bin_in) begincase (bin_in)3'b000: seg = 8'b11111101; // 03'b001: seg = 8'b01100000; // 13'b010: seg = 8'b11011010; // 23'b011: seg = 8'b11110010; // 33'b100: seg = 8'b01100110; // 43'b101: seg = 8'b10110110; // 53'b110: seg = 8'b10111110; // 63'b111: seg = 8'b11100000; // 7default: seg = 8'b11111111; // 全灭endcaseendassign seg0 = ~seg;

endmodule

波形仿真

(1)编译

verilator -Wall --trace -cc top.v --exe main.cpp

(2)生成可执行文件make -C obj_dir -f Vtop.mk Vtop

(3)生成波形

./obj_dir/Vtop

(4)查看波形

gtkwave dump.vcd

接入NVBoard

make

cd build

./top

译码器和编码器是数字系统中的常用电路,也是组合逻辑电路中的主要组成元件之一。本实验首先介绍常用的译码器和编码器的设计方法以及七段数码管的使用。本实验还将介绍Verilog语言中for循环的使用。

译码器和编码器是数字系统中的常用电路,也是组合逻辑电路中的主要组成元件之一。本实验首先介绍常用的译码器和编码器的设计方法以及七段数码管的使用。本实验还将介绍Verilog语言中for循环的使用。